What are two important design issues for cache memory. CPU loads MAR and MDR asserts Write and REQUEST.

10 Two Important Design Issues For Cache Memory Are A Speed And Volatility B Course Hero

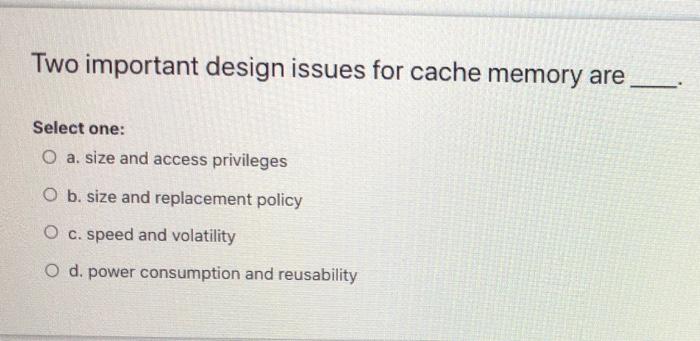

Size and replacement policy ____ operating systems are designed primarily to maximize resource utilization.

. If you are interested in this topic you can check more about Memcached. This preview shows page 1 - 2 out of 2 pages. Double Capacity Cache for Narrow-Width Data Values Modern caches are designed to hold 64-bits wide data however a proportion of data in the caches continues to be narrow width.

If a word has been altered only in the cache then the corresponding memory word is invalid. Block size is the unit of information changed between cache and main memory. Quiz 1 Two important design issues for cache memory are ____.

Therefore the cache has a shorter access time than the memory which is faster than the main memory. Size and replacement policy c. 1- Two important design issues for cache memory are ____.

Two important design issues for cache memory are ____. Power consumption and reusability d. Speed and volatility cache size and replacement policy power consumption and reusability cache size and access privileges b.

Two important design issues for cache memory are ____-size and access privileges-power consumption and reusability -size and replacement policy-speed and volatility. Coherency Correct Answer D. Two important design issues for cache memory are Select one.

Speed and volatility B. The larger the cache the larger the number of gates involved in addressing the cache. Another important concept is that of the cache memory which is also a part of the CPU.

Cache can be a really interesting and practical topic as its used in almost every system nowadays. Size and access privileges. Want this question answered.

See answer 1 Best Answer. Size and replacement policy Correct Answer. CPU loads MAR issues Read and REQUEST 2.

Main Memory asserts COMPLETE. Two important design issues for cache memory are Portray the midnight with dark midnight blue along with some smoky grey about it portraying clouds with these stars peeping out and employing studs to create constellations is simply so great. The cache memory lies in the path between the processor and the main memory.

The cache is located in the path between the processor and memory. Inclusion Exclusion Cache Memory Design Issues IEEE Internet Computing DCC. Also discussed are the size of a cache cache hierarchies fetching and replacing cache organization updating the main memory the use of two caches rather than.

How to ensure that the OS maintains control over the CPU. Key idea keyword and HOWTO Definitions. Cells and Chips Memory boards and modules Two-level memory hierarchy The cache.

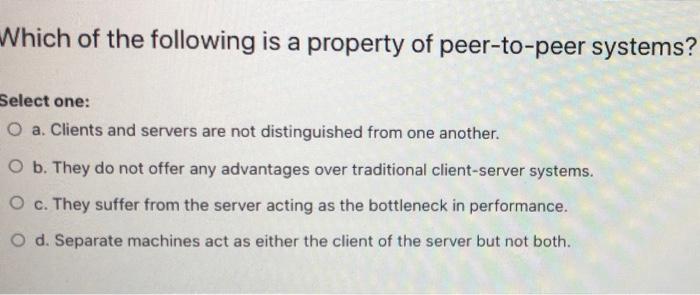

Clients and servers are not distinguished from one another. Two Important Design Issues For Cache Memory Are. The access time to the cache is 100 ns while the main access time for the memory is 700 ns.

Two important design issues for cache memory are ____. Speed and volatility O d. There are two problems to contend with.

Size and access privileges O b. Two important design issues for cache memory are. The more cache a system has the more.

After that it returns the cache back to the original server. A speed and volatility B size and replacement policy C power consumption and reusability D size and access privileges Ans. Whenever one CPU alters the data the cache of the other CPU must receive an updated version of this data.

The operation of a cache memory is described. The write policy decides on when to write back the cache block on to the main memory. Main Memory transmits words to MDR 3.

If option 1 is chosen then there is an excessive write operation. The role of cache memories and the factors that decide the success of a particular design are examined. As the block size will increase from terribly tiny to larger sizes the hit magnitude relation can initially increase as a result of the principle of localitythe high chance that knowledge within the neck of the woods of a documented word square measure possible to be documented within the close.

A power consumption and reusability B size and access privileges C speed and volatility D size and replacement policy Topic. When caches were originally introduced the typical system had a single cache. 2- A message passing model is ____.

The specification of cache parameters is considered. 1 two important design issues for cache memory are a. This is called Cache A.

Machine M may need to fetch and update the cache for A if it doesnt exist in memory. Speed and volatility b. Be notified when an answer is posted.

Virtually all modern operating systems provide support for SMP. Place the cache memory block in the main memory when it is chosen to be replaced by a new read-in block from main memory. Importance of cache memory.

More recently the use of multiple caches has become an important aspect. There are two design issues surrounding number of caches. What two important design issues for cache memory are.

The available chip and board area also limit cache size. Size and replacement policy O c. Power consumption and reusability Which of the following is a property of peer-to-peer systems.

Further if the IO device has altered main memory then the cache word is invalid. 7-1 Chapter 7- Memory System Design. Size and replacement policy.

For example an IO module may be able to read-write directly to memory. Caches are very expensive and therefore have limited capacity. The main memory has a very low access time and a very high transfer rate.

It is limited in capacity and costlier than secondary storage devices. Most contemporary designs include both on-chip and external caches. Place the cache memory block in the main memory after every update to the block.

5 CS 135 A brief description of a cache Cache next level of memory hierarchy up from register file ¾All values in register file should be in cache Cache entries usually referred to as blocks ¾Block is minimum amount of information that can be in cache ¾fixed size collection of data retrieved from memory and placed into the cache Processor generates request for. 1 More than one device may have access to main memory. What are some other terms for kernel mode.

Which of the following are important design issues of memory cache.

Cache Memory Design Geeksforgeeks

10 Two Important Design Issues For Cache Memory Are A Speed And Volatility B Course Hero

Solved Two Important Design Issues For Cache Memory Are Chegg Com

Solved Two Important Design Issues For Cache Memory Are Chegg Com

Solved Two Important Design Issues For Cache Memory Are Chegg Com

Solved Two Important Design Issues For Cache Memory Are Chegg Com

10 Two Important Design Issues For Cache Memory Are A Speed And Volatility B Course Hero

10 Two Important Design Issues For Cache Memory Are A Speed And Volatility B Course Hero

0 comments

Post a Comment